Cosa Fare Se i Powerbeats Pro Non Si Ricaricano nella Custodia

Se i tuoi Powerbeats Pro non si ricaricano, utilizza un

Qualsiasi istruzione del processore ha più fasi per il suo funzionamento. Ognuna di queste fasi richiede un singolo ciclo della CPU per essere completata. Queste fasi sono il recupero delle istruzioni, la decodifica delle istruzioni, l'esecuzione, l'accesso alla memoria e il writeback. Rispettivamente questi ottengono l'istruzione che deve essere completata, separano l'operazione dai valori su cui si opera, eseguono il processo, aprono il registro su cui verrà scritto il risultato e scrivono il risultato nel registro aperto.

Elaboratori storici in ordine

Nei primi computer, la CPU non utilizzava una pipeline di istruzioni. In queste CPU, ogni operazione a ciclo singolo doveva avvenire per ogni istruzione. Ciò significava che ci volevano cinque cicli di clock per elaborare interamente l'istruzione media prima che potesse essere avviata quella successiva. Alcune operazioni potrebbero non richiedere la scrittura di alcun risultato in un registro, il che significa che le fasi di accesso alla memoria e riscrittura possono essere saltate.

In un processore subscalare senza pipeline, ogni parte di ogni istruzione viene eseguita in ordine.

C'è un problema in agguato, tuttavia, quando si esegue un'istruzione completa in ordine prima di poter passare all'istruzione successiva. Il problema è la perdita della cache. La CPU memorizza i dati che sta elaborando attivamente nel registro. È possibile accedervi con una latenza di un ciclo. Il problema è che il registro è minuscolo perché è integrato nel core del processore. La CPU deve passare alla cache L1 più grande ma più lenta se i dati non sono già stati caricati. Se non c'è, deve andare di nuovo nella cache L2 più grande e più lenta. Il passo successivo è la cache L3; l'ultima opzione è la RAM di sistema. Ognuna di queste opzioni richiede sempre più cicli della CPU per essere verificata.

Ora, questa ulteriore latenza aggiunta può essere un grosso problema in un sistema che deve completare ogni istruzione in ordine completo prima di iniziare l'istruzione successiva. Quello che era stato un processore a 5 cicli per istruzione, può improvvisamente rimanere bloccato su un'istruzione per dozzine o centinaia di cicli di clock. Nel frattempo, non può succedere nient'altro sul computer. Tecnicamente, questo può essere in qualche modo alleviato avendo due core indipendenti. Nulla, però, impedisce a entrambi di fare la stessa cosa, potenzialmente contemporaneamente. Quindi seguire il percorso multi-core non risolve questo problema.

La pipeline RISC classica

RISC è l'acronimo di Computer a set di istruzioni ridotto . È uno stile di progettazione del processore che ottimizza le prestazioni semplificando la decodifica di ogni istruzione. Questo è in confronto a CISC o Complex Instruction Set Computer, che progetta set di istruzioni più complessi consentendo la necessità di un minor numero di istruzioni per eseguire le stesse attività.

Il classico design RISC include una pipeline di istruzioni. Invece di eseguire una qualsiasi delle cinque fasi di istruzione in un dato ciclo, la pipeline consente l'esecuzione di tutte e cinque le fasi. Naturalmente, non è possibile eseguire tutte e cinque le fasi di un'istruzione in un ciclo. Ma puoi mettere in coda cinque istruzioni consecutive con un offset di uno stadio ciascuna. In questo modo è possibile completare una nuova istruzione a ogni ciclo di clock. Offrendo un potenziale aumento delle prestazioni di 5 volte per un aumento relativamente basso della complessità del core.

In un processore pipeline scalare, ogni fase dell'esecuzione di un'istruzione può essere eseguita una volta per ciclo di clock. Ciò consente un throughput massimo di un'istruzione completata per ciclo.

I processori che non dispongono di una pipeline possono essere solo sub-scalari, poiché non possono eseguire un'istruzione completa per ciclo. Con questa pipeline primaria in cinque fasi, puoi creare una CPU scalare in grado di completare un'istruzione per ogni processo. Creando pipeline ancora più estese, puoi realizzare CPU superscalari in grado di eseguire più di un'istruzione per ciclo di clock. Naturalmente, ci sono ancora potenziali problemi.

Ancora sequenziale

Niente di tutto ciò risolve il problema di attendere molti cicli per una risposta quando è necessario interrogare i diversi livelli di cache e RAM. Introduce anche un nuovo problema. Cosa succede se un'istruzione si basa sull'output dell'istruzione precedente? Questi problemi vengono risolti in modo indipendente con un dispatcher avanzato. Pianifica attentamente l'ordine di esecuzione in modo che nessuna istruzione che si basa sull'output di un'altra sia troppo ravvicinata. Gestisce anche i cache miss parcheggiando un'istruzione e sostituendola nella pipeline con altre istruzioni che sono pronte per essere eseguite e non richiedono il suo risultato, riprendendo l'istruzione quando è pronta.

Queste soluzioni possono funzionare su processori senza pipeline, ma sono necessarie per un processore superscalare che esegue più di un'istruzione per clock. Un predittore di ramo è anche molto utile in quanto può tentare di prevedere l'esito di un'istruzione con più di un risultato potenziale e continuare a presumere che sia corretto fino a prova contraria.

Conclusione

Una pipeline consente di utilizzare tutte le capacità distinte del processore in ogni ciclo. Lo fa eseguendo contemporaneamente diverse fasi di diverse istruzioni. Questo non aggiunge nemmeno molta complessità al design della CPU. Inoltre apre la strada per consentire a più di un'istruzione di eseguire una singola fase per ciclo.

Se i tuoi Powerbeats Pro non si ricaricano, utilizza un

Mantenere le attrezzature in buone condizioni è fondamentale. Ecco alcuni utili suggerimenti per mantenere la tua stampante 3D in condizioni ottimali.

Come abilitare la scansione sulla Canon Pixma MG5220 quando si esaurisce l

Scopri alcune delle possibili cause per cui il tuo laptop si surriscalda, insieme a suggerimenti e trucchi per evitare questo problema e mantenere il tuo dispositivo fresco.

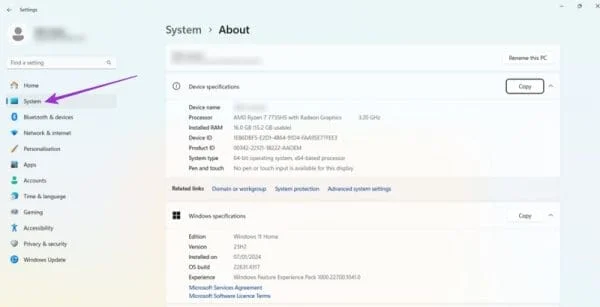

Ti stai preparando per una serata di gioco, ed è una grande serata - hai appena acquistato "Star Wars Outlaws" sul servizio di streaming GeForce Now. Scopri l

Mantenere le stampanti 3D è molto importante per ottenere i migliori risultati. Ecco alcuni consigli importanti da tenere a mente.

Hai difficoltà a scoprire quale indirizzo IP sta utilizzando la tua stampante? Ti mostreremo come trovarlo.

Se non sei sicuro se acquistare gli AirPods per il tuo telefono Samsung, questa guida può sicuramente aiutarti. La domanda più ovvia è se i due siano compatibili.

Scopri come configurare Spotify sul tuo Garmin Venu per ascoltare la tua musica preferita mentre ti alleni.

Scopri come risolvere i problemi dell